電気回路/HDL/VivadoのXDC制約文法

Vivado の制約文法は ISE と異なる†

今までの UDC ファイルをXDCに直さなければならないらしいです。

情報源†

日本語版は版が古いので、利用する際には英語版の更新履歴をチェックする必要がありそうです。

- Vivado Design Suite ユーザー ガイド - 制約の使用

- ISE から Vivado Design Suite への移行ガイド - 第3章 UCF制約のXDCへの移行

- FPGA の部屋 - vivado :http://marsee101.blog19.fc2.com/category94-14.html

制約ガイドは論理だっていないし例も少ないしで非常に読みにくいです。

むしろ移行ガイドの3章を見ると、XDC文法の概略を見渡せるようです。 むしろこれ、UDC文法のガイドとしても役立ちそう。。。

tcl入門†

XDC ファイルは tcl として実行可能なプログラムソースになっています。

このあたりが分かりやすそう。

ただし、次の制約があります。

XDC フ ァ イルで使用可能なビル ト イ ン Tcl コマン ドは、 set、 list、 および expr のみです。

concat とかも使えないようですね。。。

[DRC 23-20] Rule violation (CFGBVS-1)†

新規プロジェクトを作成して bitstream を生成したところ、 次のような警告が表示されました。

[DRC 23-20] Rule violation (CFGBVS-1) Missing CFGBVS and CONFIG_VOLTAGE Design Properties - Neither the CFGBVS nor CONFIG_VOLTAGE voltage property is set in the current_design. Configuration bank voltage select (CFGBVS) must be set to VCCO or GND, and CONFIG_VOLTAGE must be set to the correct configuration voltage, in order to determine the I/O voltage support for the pins in bank 0. It is suggested to specify these either using the 'Edit Device Properties' function in the GUI or directly in the XDC file using the following syntax:

set_property CFGBVS value1 [current_design] #where value1 is either VCCO or GND

set_property CONFIG_VOLTAGE value2 [current_design] #where value2 is the voltage provided to configuration bank 0

Refer to the device configuration user guide for more information.

このエラーの対処は制約ガイドには載っていません。 「制約」ではなく「設定」のようです?

こちらに解説を見つけました。 http://japan.xilinx.com/support/answers/57045.html

例えば、次のように設定します。

set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design]

設定内容は XDC ファイルに直接記述しても良いですが、

によれば、Flow Navigator で Synthesized Design を開いた状態で、 メニューの [Tools]-[Edit Device Properties...]-[Configuration]-[Configuration Setup] に対応する項目がありますので、GUI で設定することも可能です。

ピン配置の指定†

LANGUAGE:tcl set_property PACKAGE_PIN T20 [get_ports switch1] set_property IOSTANDARD LVCMOS33 [get_ports switch1] set_property PULLDOWN true [get_ports switch1] set_property PROHIBIT true [get_sites Y11]

クロックの指定†

LANGUAGE:tcl create_clock -period 20 [get_ports clk]

マルチクロック制約†

LANGUAGE:tcl

set_multicycle_path -setup -to [get_pins -match_style ucf {*/myip/result_of_complex_calculation_reg[*]/D}] 16

set_multicycle_path -hold-to [get_pins -match_style ucf {*/myip/result_of_complex_calculation_reg[*]/D}] 16

get_cells に -match_style ucf を付けることでフルパスに対するマッチを行える。

デフォルトの -match_style sdc では * が / にマッチしないため、先頭の */ が役に立たない。

もっと複雑なマッチを行いたければ regexp を使える。

LANGUAGE:tcl

set_multicycle_path -setup -to [get_pins -match_style ucf -regexp {.*/myip/result[1-3]_reg\[\d+\]/D}] 16

set_multicycle_path -hold -to [get_pins -match_style ucf -regexp {.*/myip/result[1-3]_reg\[\d+\]/D}] 16

これで、result1, result2, result3 にマッチさせることができるのだけれど、 [ や ] をエスケープしなければならないのがちょっと面倒。

foreach などを使える?†

xdc ファイルは tcl 言語っぽい見た目なので、以下のように複数のレジスタへの指定を foreach を使ってまとめて書いたりもできる・・・のかと思うのだけれど、 上で書いたとおり xdc ファイルにそのまま書いたのでは

[Designutils 20-1307] Command 'foreach' is not supported in the xdc constraint file.

というエラーが出て使えない。

https://www.xilinx.com/support/answers/59134.html

を見て分かったことには、新たに拡張子を .tcl とした、 例えば system_xdc.tcl などというファイルをテキストエディタで作って、 add source から constraint ファイルとして追加すると問題なく使える。

GUI で制約の設定ができなくなること以外にはデメリットはなさそうなので、 どんどん使っていきたい。

LANG:tcl

# このコードを使うには拡張子 .tcl の制約ファイルにしなければなりません。

foreach reg {

{result[1-4]_reg\[\d+\]}

{some_other1_reg}

{some_other2_reg}

{some_other3_reg}

} {

set_multicycle_path -setup -to [get_pins -match_style ucf -regexp ".*/some_internal_instance_implemented_in_myip/$reg/D"] 32

set_multicycle_path -hold -to [get_pins -match_style ucf -regexp ".*/some_internal_instance_implemented_in_myip/$reg/D"] 32

}

あー、ただし、この制約指定用途の .tcl ファイルはカスタム IP には含められないようなので、 これはメインプロジェクトでのみ使えるテクニックになります。

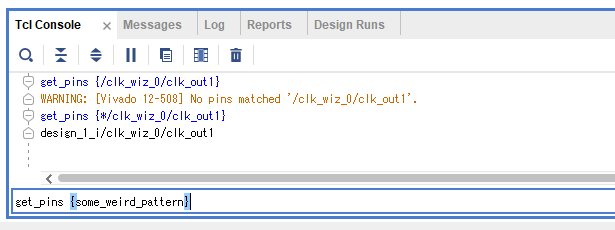

get_cells や get_pins が "no cells/pins matched" になってしまうとき†

set_property などは、対象となるオブジェクトを get_pins や get_cells で指定するのだけれど、しばしば get_pins/get_cells に与える引数に間違いがあって、 目的のオブジェクトが引っかからないことがある。

そういった場合には

[Vivado 12-1387] No valid object(s) found for set_multicycle_path constraint with option '-from [get_pins some_wrong_matching_pattern]'.

のようなエラーが出て、正しく制約がかからない。

こういった場合に get_pins や get_cells に与えるパターンをちょっと変えては synthesize & implement するような方法でデバッグしていては短い人生すぐに終わってしまうので、 synthesize が終わった状態で tcl コンソールを開いて、 そこに get_cells や get_pins コマンドを入力すれば 時間を掛けずにマッチングパターンのデバッグができる。

-hierarchical が必要かも†

XDC では ucf と違って * が / にマッチしないので、複数階層にわたって get_xxx したい場合には -hierarchical オプション (短縮形は -hier)を付ける必要があります

https://japan.xilinx.com/support/answers/62136.html

その他、可能なオプションの一覧はこちら: