Xilinx Memory Interface Generator (MIG) による DDR2 SDRAM のアクセス の履歴(No.2)

更新- 履歴一覧

- 差分 を表示

- 現在との差分 を表示

- ソース を表示

- 電気回路/HDL/Xilinx Memory Interface Generator (MIG) による DDR2 SDRAM のアクセス へ行く。

概要†

以下の内容はまだ試行錯誤中のもので、間違っている可能性が多分にあります。

紛らわしい記事ですみません。

一応、Xilinx FPGA から DDR や DDR2、DDR3 といった高速メモリにアクセスするために、 Memory Interface Generator (MIG) というソフトを使ってIPコアを生成する方法と、 生成したIPコア経由で Spartan 3A DSP から DDR2 メモリにアクセスする方法をまとめる予定です。

詳細としては、

Core name: Xilinx MIG Version: 3.3 Release Date: December 2, 2009

を使って、

Spartan 3A DSP 1800 Starter Platform

用のコアを作成し、その使い方について調べたものです。

入出力ポートを指定してコアを生成する†

まずは MIG を使ってIPコアを生成する方法についてなのですが、 一見簡単そうに見えて、思ったよりも難しかったです。

- Xilinx の Reference Board 用にコアを作る方法

- FPGA とメモリとの間をどのように結線すべきか MIG に決めてもらう方法

は簡単に分かったのですが、Starter Platform を買った場合のように PCBがすでにできていて、MIG が想定するのと異なるピン配置で FPGA がメモリと接続されている場合に使えるコアを どのように生成すればよいかが分かりにくかったので、 以下に手順をまとめておきます。

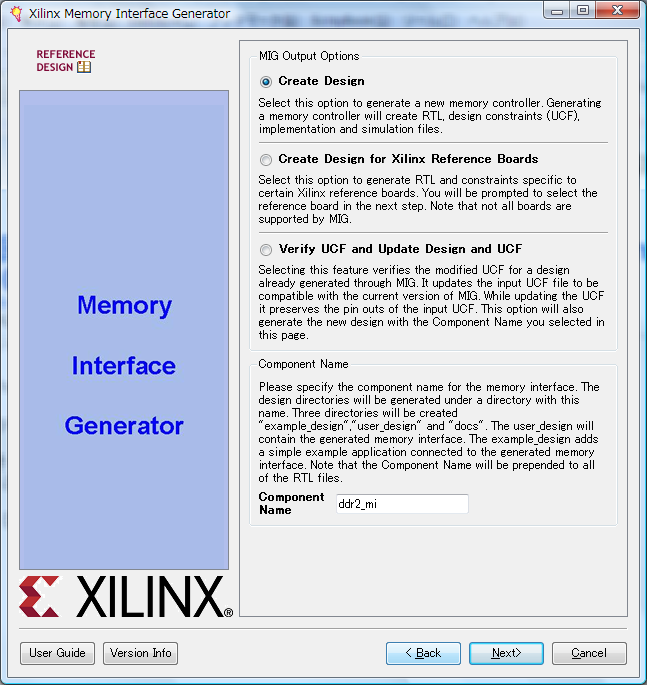

MIG の2ページ目で [Create Design] を指定する†

MIG を起動した際の一番目の選択肢です。

最終的には Verify UCF and Update Design and UCF を使うのですが、 まだ .ucf がないので、ここでは一旦 [Create Design] を選びます。

メモリの仕様に合わせてオプションを選択する†

Spartan 3A DSP 1800 Starter Platform 用に次のように指定しました。

自信のないところもあるのですが、、、

うまく行かなかったらまた考えます。

| Memory Selection | DDR2 SDRAM |

| Frequency | 8000 ps = 125MHz |

| Write Pipe Stages | 4 |

| Memory Type | Components |

| Memory Part | MT47H32M16-3 |

| Data Width | 64 |

| Data Mask | Check |

| Burst Length | 4 |

| Burst Type | sequential |

| Output Drive Strength | Fullstrength |

| RTT(nominal)-ODT | 150ohms ? |

| DQS# Enable | Enable |

| Use DCM | Uncheck |

| Class for Address and Control | Class II |

| Class for Data | Class II |

| Debug Signals for Memory Controller | Disable |

Available/Reserved ピンは指定しない†

つぎにピン配置を決めるのですが・・・

[Create Design] モードというのは、新たにPCBを起こす際に MIG にお勧めの結線方法を提案してもらうというモードなので、 メモリとの接続に使ってもよいピンを MIG に教えると、 MIG がピン配置を勝手に決め、その配置でコアを生成するという 話になっています。

デフォルトでは全てのピンが Available Pins に入っていて、 MIG はその中から適当なピンを選んでコアを生成します。

そういう話ですので、このモードではどんなに頑張っても 1つ1つのピン配置をこちらから指定することはできません。

もちろんそれでは困るのですが、 どうしようもないので後で直すことにして、 ここではそのままにしておきます。

ちなみに、このページの [Read UCF File] は他の用途に使っているために メモリとの配線に使えない Reserved Pins を指定するためのもので、 メモリとの配線方法を指定するためのものでは無いので、 押しても役に立ちません。

Bank もこの時点では気にしない†

MIG は Available Pins から適当なピンを選んで信号線を割り当てますが、 このページでは信号線の種類毎に、使う Bank を指定することができます。

繰り返しになりますが、この時点ではピン配置を気にする必要は無いので、 すべてのピンが割り当てられるまでチェックを増やしていけばOKです。

デフォルトでは Address ピンの割り当てがうまくできていなかったので、 Bank1 の Address/Control をチェックすることで、 すべてのピンを割り当てました。

コアを生成する†

どんどんページをめくって、最後にライセンスを承諾するとコアが生成されます。

ピンを指定するための ucf ファイルを作る†

ここからいよいよピン配置を指定する段階です。

私の場合 ddr2mi という名前でコアを作ったのですが、 できたコアは以下のディレクトリにありました。

(project folder)/ipcore_dir/ddr2mi/user_design

このフォルダの par/ddr2mi.ucf に、MIG が適当に決定したピン配置と、 そのピン配置に最適化された回路を生成するための ucf ファイルが作成されています。

このファイルから #bank というコメントが付いている行を抜き出すと、 ピン配置を指定している部分を抽出できます。

unix ライクなコンソールが使えれば、

LANG:console $ grep "#bank" ipcore_dir/ddr2mi/user_design/par/ddr2mi.ucf | sort > ddr2mi_pins.ucf

とすることで、

ddr2mi_pins.ucf

NET "cntrl0_ddr2_a[0]" LOC = "J21" ; #bank 1 NET "cntrl0_ddr2_a[10]" LOC = "B2" ; #bank 3 NET "cntrl0_ddr2_a[11]" LOC = "H7" ; #bank 3 NET "cntrl0_ddr2_a[12]" LOC = "G6" ; #bank 3 ... NET "cntrl0_ddr2_dqs_n[6]" LOC = "J4"; #bank 3 NET "cntrl0_ddr2_dqs_n[7]" LOC = "J6"; #bank 3 NET "cntrl0_rst_dqs_div_in" LOC = "G4"; #bank 3 NET "cntrl0_rst_dqs_div_out" LOC = "F5"; #bank 3

のようなファイルができます。

これを自分のボードに合わせて編集し、正しいピンを指定します。

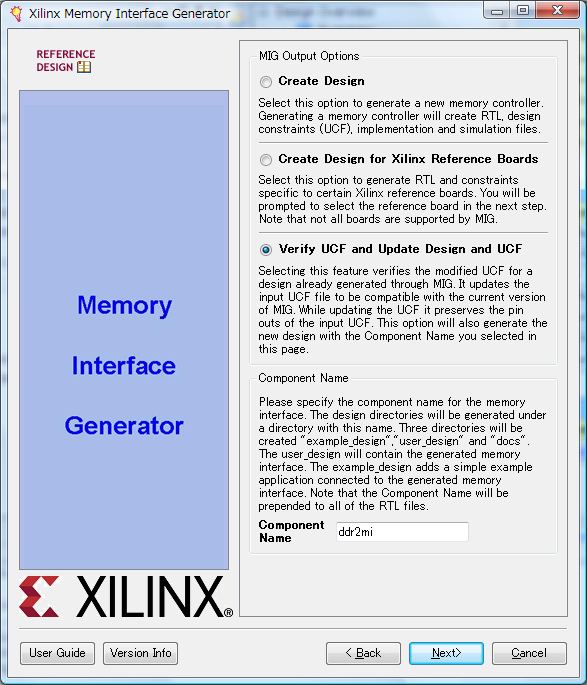

ucf ファイルを元にコアのピン配置を変更する†

指定したピン配置を元に、FPGA 内部のプリミティブの配置も変更しなければ ならないのですが、手作業では無理なので、もう一度 MIG を起動してコアを再生成します。

Design ペインの Hierarchy で先ほど生成した ddr2mi をダブルクリックして MIG を起動します。

今度は [Verify UCF and Update Design and UCF] を選択し、

Load Prj File に ipcore_dir/ddr2mi/user_design/mig.prj

Load UCF File に ddr2mi_pins.ucf

を指定します。

Next を連打して、もう一度ライセンス条項を許諾すると、 指定したピン配置でコアを生成できます。

正しいピン配置になっているかどうか確認する†

LANG:console $ grep "#Bank" ipcore_dir/ddr2mi/user_design/par/ddr2mi.ucf | sort > ddr2mi_pins.ucf

としてみると、指定したとおりのピン配置でコアが生成されていると思います。

MIG の生成したコアを使う†

まだ準備段階です。

ボードに載っているメモリは Micron の MT47H32M16BM-3 だそうです。

モードレジスタの値†

ddr2mi_parameter_0.v によれば、

LOAD_MODE_REGISTER 13'b0010100110010

となっていますので、これをメモリのデータシートと突き合わせると、

| 項目 | 値 | 意味 |

| Mode Register Definition | 00 | Mode register (MR) |

| PD Mode | 0 | Fast exit |

| Write Recovery | 010 | 3 |

| DLL Reset | 1 | Yes |

| Test Mode | 0 | Normal Mode |

| CAS# | 0 | |

| CAS Latency (CL) | 11 | 3 |

| Burst Type | 0 | Sequential |

| Burst Length | 010 | 4 |

という設定であることが分かりました。